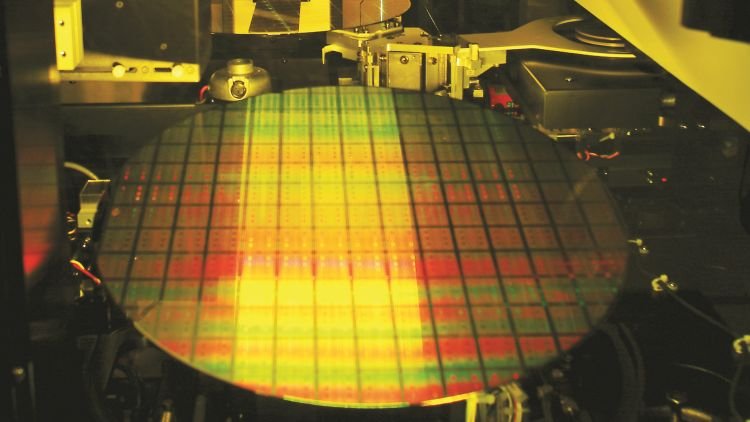

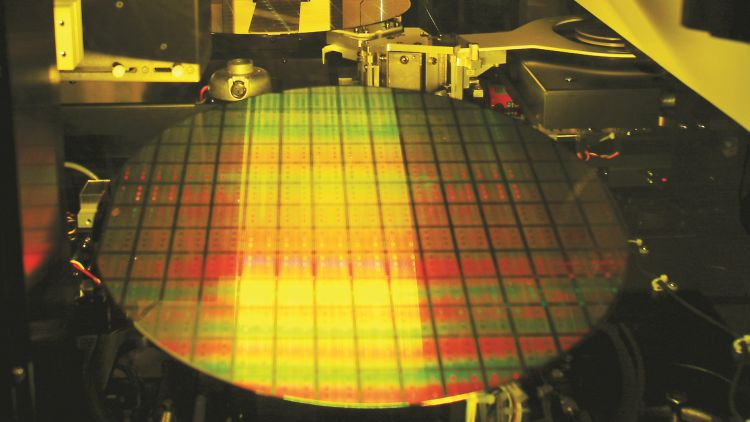

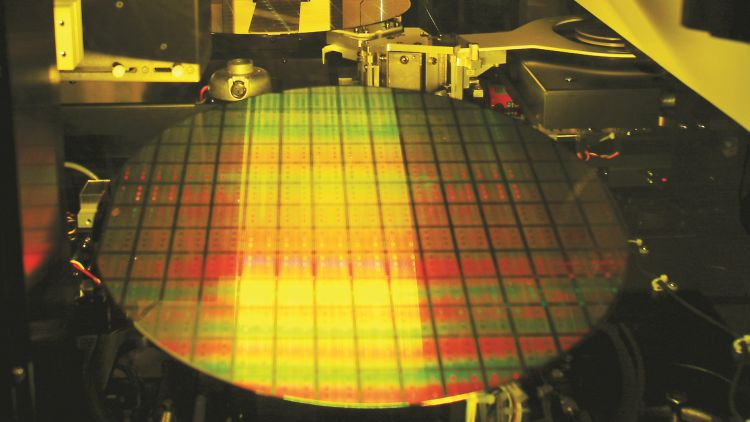

Представители TSMC не раз подчёркивали, что общее создание 3-нм продукции будет развёрнуто во 2-ой половине текущего года, и подготовка идёт по плану. Отлично знакомая структура транзисторов FinFET дозволит избежать сюрпризов, но количество слоёв, обрабатываемых с помощью EUV-литографии, придётся прирастить. На данный момент компания задумалась над тем, как ограничить их количество разумным числом.

Как объясняют тайваньские СМИ (Средства массовой информации, масс-медиа — периодические печатные издания, радио-, теле- и видеопрограммы), возрастающая интенсивность использования литографических сканеров со сверхжёстким ультрафиолетовым излучением (EUV) наращивает расходы TSMC, так как одна таковая система стоит наиболее $100 млн, а их приходится закупать десятками. На самом деле, TSMC на данный момент покупает наиболее половины всех EUV-сканеров, выпускаемых холдингом ASML. Растущие издержки безизбежно придётся перекладывать на себестоимость продукции и её отпускную стоимость для заказчиков. В рамках освоения 3-нм технологии TSMC пробует мало сберечь, понижая количество слоёв полупроводниковых компонент, изготавливаемых с внедрением EUV.

Внедряя 7-нм техпроцесс, компания TSMC начала с четырёх слоёв, использующих EUV, последующим шагом стал 6-нм техпроцесс с пятью слоями, а к моменту освоения 5-нм технологии их количество подросло до 14 либо 15 штук. Ожидается, что 3-нм техпроцесс может востребовать использования до 25 слоёв с EUV-литографией, и на данный момент TSMC пробует уменьшить это количество до 20, чтоб понизить издержки и себестоимость продукции.